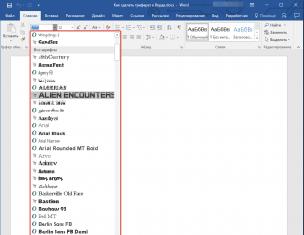

Слайд 2

ЦМТ

Цифровое моделирование рельефа составляет крупный раздел внутри блока обработки данных в ГИС и также относится к задачам геоанализа и моделирования. Хотя оно реализовано далеко не во всех ГИС-пакетах, тем не менее цифровое моделирование рельефа – одно из приоритетных направлений развития современной геоинформатики.

Слайд 3

Рельеф как объект ЦМТ

Рельеф является главным элементом ландшафта. Он определяет все особенности местности: характер и конфигурацию гидрографической сети, распределение растительности и почвенного покрова, микроклимат и экологические условия, расположение дорог и населенных пунктов

Слайд 4

Цифровое моделирование рельефа ставит перед собой две главные группы задач: Первая сводится к разработке методов и приемов по созданию цифровых моделей рельефа (ЦМР); Вторая совершенствует способы их практического использования.

Слайд 5

Создание ЦМР. Общий прицип

X Y Z z3 z1 z2 x1 x3 x2 y1 y2 y3 1 2 3 ID X Y Z 1 x1 y1 z1 2 x2 y2 z2 3 x3 y3 z3 … … … … n xn yn zn Цифровая модель рельефа (ЦМР)

Слайд 6

Создание ЦМР

Современные цифровые модели рельефа создаются четырьмя основными способами: получение высотных отметок в узлах регулярной сетки нерегулярное (случайное) размещение высотных отметок в узлах произвольной сети размещение высотных отметок вдоль горизонталей или изобат с определенным шагом получение высотных отметок в точках пересечения горизонталей со структурными линиями рельефа

Слайд 7

Получение высотных отметок в узлах регулярной сетки

Слайд 8

Нерегулярное размещение высотных отметок в узлах произвольной сети

Слайд 9

Размещение отметок вдоль горизонталей с определенным шагом

Слайд 10

Получение отметок в точках пересечения горизонталей со структурными линиями рельефа

Слайд 11

Источник данных для ЦМР

Главными источниками для создания ЦМР служат крупномасштабные топографические карты. Типовая технология создания ЦМР основана на цифровании (обводке) горизонталей как основной ее составляющей и высотных отметок. Применение мелкомасштабных карт ограничено по условиям генерализации. На таких картах геометрическая точность вступает в противоречие с географическим правдоподобием и морфологическим соответствием, и, как правило, метричностью жертвуют. В теории и практике геоинформатики доказывается, что использование в качестве исходных материалов для построения ЦМР карт масштаба 1: 500 000 и мельче, – бессмысленно.

Слайд 12

Форматы ЦМР

Обычно первичные данные для создания новой ЦМР (получаемые традиционно по картам) приводятся к одному из двух наиболее широко распространенных формата представления: GRID-модели и TIN-модели. Первая модель во многом аналогична растровой модели пространственных данных: она предполагает разбиение пространства карты на далее неделимые элементы (пикселы), внутри которых высота земной поверхности считается постоянной. Пикселы образуют квадраты регулярной обычно прямоугольной матрицы высот, расстояние между которыми определяет пространственное разрешение ЦМР.

Слайд 13

GRID.1

При создании GRID-моделей на первом шаге изучаемую территорию как бы нарезают на квадратные выделы, участки, геометрические размеры которых определяются заранее исходя из качества исходных материалов, задач исследования и технических средств (grid в переводе с английского – решетка, сетка). Малые пиксели детальнее передают неровности земной поверхности, но для создания таких ЦМР требуются крупномасштабные исходные материалы, а образованный массив чисел – огромен и труднообрабатываем. Обычно размер пикселей устанавливают равным 1 – 2 мм в масштабе карты (например, для 1: 100 000 карты размер пиксела – 100 – 200 м на местности). l = 1 – 2 мм

Слайд 14

GRID.2

Слайд 15

GRID.3

Затем по правилам интерполяции определяются значения высот всех прочих пикселов. Рельеф имитируется плотно подогнанными друг к другу параллепипедами разной высоты.

Слайд 16

GRID.4

Слайд 17

GRID. Rezult

Слайд 18

TIN.1

Суть модели TIN – в ее названии: Triangulated irregular network (нерегулярная треугольная сеть). Она представляет собой сеть треугольников, в вершинах которых находятся высотные отметки. Строится она следующим образом. Все точки с известными высотами соединяются попарно отрезками так, чтобы они нигде не пересекались; в противном случае оставляют кратчайший отрезок. Полученная сеть треугольников в топографии получила название элементов триангуляции Делоне. В начертательной геометрии с триангуляцией Делоне тесно связаны полигоны Тиссена, или диаграммы Вороного, обладающие рядом особых свойств. В результате моделируемая поверхность представляется как многогранная.

Слайд 19

TIN.2

X Y Z трехреберные грани

Слайд 20

TIN.4

Слайд 21

Слайд 22

Слайд 23

Интерполяция в ЦМР

Важным элементом построения любой ЦМР независимо от формата представления является интерполирование – т.е. нахождение высот земной поверхности любой произвольной точки, для которой известны только плановые координаты X и Y, по некоторой сети опорных точек, называемых узлами интерполяции, для которых известны все три координаты – X,Y и Z. Для GRID-моделей интерполяция необходима для получения непрерывной матрицы высот по дискретным необязательно регулярным опорным точкам, в TIN-моделях она применяется с целью сгущения сети треугольников, обычно весьма разреженной. Все методы интерполяции делятся на глобальные и локальные, а также точные и аппроксимирующие.

Слайд 24

Глобальная инетполяция

При глобальной интерполяции определение высот произвольных точек осуществляется с использованием всех узлов интерполяции. В этом случае изменение в исходном наборе опорных точек (добавление, удаление и т.п.) сказывается на всей результирующей ЦМР. глобальная интерполяция

Слайд 25

Локальная интерполяция

В локальной интерполяции расчет высоты ведется лишь в непосредственных окрестностях точки, многократно повторяя алгоритм вычисления в разных частях ЦМР. локальная интерполяция

Слайд 26

Аппроксимирующая интерполяция

В основе аппроксимирующих методов лежит соображение о неточности или даже ошибках исходных данных, потому они отражают лишь общий тренд поверхности, не воспроизводя точного значения высоты в опорных точках.

Слайд 27

Точная интерполяция

Точные методы интерполяции сохраняют высоты в опорных точках, на которых базируется сама интерполяция, и поверхность проходит через все точки с известными аппликатами.

Слайд 28

Linear interpolation

Среди конкретных реализаций алгоритмов интерполяции наиболее часто употребляется линейная интерполяция, выполняемая от точки к точке по отрезкам прямых линий. z x или y 1 2 3 4 5 6 7 8 9 10 порядковые номера ячеек растра d d0 z1 z2 z0 z0 = z1 + (z2 – z1) · d0 / d

Слайд 29

Inverse weight interpolation

Другой метод – метод обратных весовых коэффициентов – при интерполировании позволяет в большей степени учитывать влияние близ лежащих точек и в меньшей – находящихся на удалении. z x или y 1 2 3 4 5 6 7 8 9 10 порядковые номера ячеек растра d2 z1 z2 z0 z0 = (d1 · z1 + d2 · z2) / (d1 + d2) d1

Слайд 30

Nearest neighbor interpolation

В следующем способе – методе ближайшего соседа – высота точки принимается равной высоте опорной точки, располагающейся ближе всего. z x или y 1 2 3 4 5 6 7 8 9 10 порядковые номера ячеек растра d2 z1, z0 z2 z0 = z1 |если d1

Слайд 31

Spline interpolation

Следующий метод интерполяции получил названия метода сплайнов (splineв переводе с английского – упругая линейка), или кусочно-полиномиального сглаживания.

Слайд 32

концы отрезков криволинейные отрезки сплайна f3´(z, x[y]) f1(z, x[y]) f2(z, x[y]) f3(z, x[y]) f4(z, x[y]) f5(z, x[y]) f1´´(z, x[y]) z x или y z x или y 1 2 3 4 5 6 7 8 9 10 порядковые номера ячеек растра z1 z2 z0 z0 = f(z, x[y]) x[y]1 z3 z4 x[y]2 x[y]3 x[y]4 f(z, x[y])

Слайд 33

Аппроксимирующая интерполяция

Все рассмотренные методы интерполяции относятся к точным. Однако наибольшую популярность завоевали аппроксимирующие методы: полиномиальная интерполяция кригинг.

Слайд 34

В аппроксимирующих методах рельеф земной поверхности понимается как очень сложная функция вида z = F(x, y), т.е. высота точки зависит от ее пространственного положения. Эта функция неизвестна и неопределима, поскольку учитывает огромное число причин и факторов, влияющих на рельеф. Но ее можно заменить более простой функцией, свойства которой известны, и представить рельеф в виде z = f(x, y) + ε, где ε– некоторый неразложимый остаток, очень малый по величине: = ε→ 0.

Слайд 35

Полиноминальная интерполяция

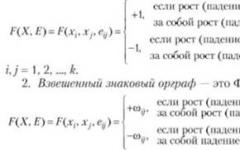

В полиномиальной интерполяции отыскание высот промежуточных точек z0 проводится путем решения полиномов заданной степени m: где aij– коэффициенты полинома, а x и y – координаты сети. Коэффициенты полинома определяются исходя из условия минимизации ε, для этого необходимо, чтобы число опорных точек, привлекаемых для расчета, было не меньше величины (m + 1)·(m + 2) / 2. Порядок полинома указывает на число чередующихся максимумов или минимумов аппроксимирующей поверхности, которое равно m – 1.

Слайд 39

Кригинг.1

В методе кригинга изменчивость высот подразделяется на три компоненты: трендовую e автокорреляционную e´ случайнуюe´´ На примере одномерной функции значения высот z в точках x может быть представлено как: z(x)= e(x) + e´(x) + e´´(x).

Слайд 40

Кригинг.2

Трендовая компонента отражает направленность изменений высот Автокорреляционная характеризуют физически трудно объяснимую вариацию, зависящую от соседних точек Случайная – некоторый статистический шум, равный постоянному значению. Различают простой кригинг и универсальный. В простом кригинге тренд e(x) предполагается постоянным и рассматривается как средняя арифметическая высота. В универсальном кригинге тренд обычно моделируется полиномами первой или второй степени.

Слайд 41

Кригинг.4

z x z x e(x) e´(x) e´´(x) z(x) = e(x) + e´(x) + e´´(x)

Посмотреть все слайды

Понятие логического моделирования Под логическим моделированием понимают полное и точное программное воспроизведение поведения цифровой схемы по ее функциональному и/или структурному описанию и заданным наборам входных сигналов. При ручном проектировании модель представляется действующим макетом или опытным образцом (прототипом). При автоматизированном проектировании действующий макет заменяется имитационной (программной) моделью проекта, а натурные или физические эксперименты – модельными (машинными). В модель легко вносить любые изменения и таким образом улучшать проект до тех пор, пока он не достигнет требуемого качества.

Задачи, решаемые методом логического моделирования 1.Основная задача логического моделирования - проверить правильность функционирования цифровой схемы до её фактического (физического) воплощения 2.Исследование временных характеристик схемы - быстродействия, времени выполнения операций, максимальных частот счёта или сдвига. Обнаружение состязаний и рисков сбоя. Задержки. 3.Контроль временных соотношений - времени предустановки и времени удержания, минимальной длительности сигналов. 4.Разработка контролирующих и диагностических тестов. Моделирование неисправностей. 5.Сравнение альтернативных вариантов схемных решений и выбор наиболее подходящего. «Тирания альтернатив». До 70% времени работы над проектом тратится именно на его верификацию

Задачи, решаемые методом логического моделирования 6.Контроль выходов компонентов на допустимую нагрузку. 7.Контроль компонентов схемы на допустимую мощность рассеяния. 8.Выявление не устанавливаемых элементов по сигналам сброса или начальной инициализации. 9.Выполнение статистических оценок, например определение процента выхода годных схем, которые невозможно сделать на единичных опытных образцах. 10.Проведение климатических, чаще всего температурных испытаний.

Процесс логического моделирования Моделирование выполняется аналогично проверке схемы вручную. Экспериментируя с действующим макетом, инженер устанавливает уровни напряжений на входах схемы и наблюдает выходные сигналы на экране осциллографа. В случае логического моделирования он имитирует эти действия с помощью специальной программы, называемой моделятором (симулятором, имитатором). Разница в том, что реальные, физические сигналы заменяются программно генерируемыми и наблюдаются они не на осциллографе, а на экране монитора.

Процесс логического моделирования С точки зрения обработки данных моделирование сводится к трём основным процессам: Составление описания моделируемой схемы на некотором языке (ЯОО - язык описания объектов) и ввода его в ЭВМ. Описание можно задать в виде схемы, списком компонентов и связей (NetList), в форме табличного представления, в виде диаграммы состояний ЦА. Контроль описания (например, поиск плавающих входов, закороченных выходов, дублированных имён) и трансляция его в объектный код. Программа контроля ERC – Electrical Rules Check. Выполнение экспериментов с программной моделью, имитирующей работу схемы. Перед началом моделирования задаются наборы входных сигналов, исходное состояние схемы, контрольные точки для наблюдения, конечное время моделирования.

Графическое представление процесса логического моделирования Ввод описания схемы NetList Библиотеки графических описаний компонентов Автоматическая генерация модели схемы Библиотеки математических моделей компонентов ЯОО Проектировщик & Y=A and B; Модель схемыМоделятор proceduremain Инструментальные средства моделирования Диаграммы входных сигналов Исходное состояние схемы Управление выводом Специальные условия Метод моделирования Результаты моделирования Рабочая программа ЯОЗ M1 – принцип дельта T M2 – принцип дельта Z min typical max температура неисправности Компилирующее моделирование Компоновщик Линковщик

Модели цифровых сигналов Круг задач, решаемых методом логического моделирования, определяется в первую очередь числом различимых состояний, которые может принимать цифровой сигнал. Каждому состоянию сопоставляется свой индивидуальный символ, а их совокупность составляет алфавит моделирования. Простейший алфавит - двоичный, используемый в старых АСМ, содержал битовый набор {0, 1}. Так как в этом случае любой сигнал может принимать только два значения (0 и 1), то смену логического уровня вынужденно приходилось считать мгновенной. Реальный сигнал Порог Двоичная аппроксимация Событие – мгновенное переключение Достоинство – экономичность. Позволяет решать только одну главную задачу моделирования – проверить работу схемы

Модели цифровых сигналов При троичном моделировании {0, 1, Х} переключающийся сигнал можно изобразить более реалистично, например 0Х1 или 1Х0. Такая запись означает, что при смене состояния элемента его выходной сигнал в течение некоторого времени (пока формировался фронт или спад) имел неопределенное значение. 0 1 X Переключение 0X1 Переключение 1X0 0 1 X 0X1 Active-HDL 8.1 X – неизвестное значение Трёхзначный алфавит {0,1,X} используется в языке PML (САПР PCAD 4.5) X присваивается сигналу на выходе ЛЭ во время переходного процесса. X присваивается выходам триггера после подачи на его входы запрещённых комбинаций сигналов X присваивается выходам триггера в начале моделирования, когда его состояние неизвестно

Модели цифровых сигналов При моделировании компонентов с динамическими входами (триггеры, счётчики, регистры, память) очень удобно фиксировать моменты переключения сигналов в том или ином направлении. С этой целью в алфавит моделирования добавляются ещё два значения: или / или R (от слова Rise - фронт) - переключение сигнала вверх; или \ или F (от слова Fall - спад) - переключение сигнала вниз. В САПР OrCAD 9.1 (PSpice проекты) используется шестизначный алфавит {0,1,X,R,F,Z}

Модели цифровых сигналов Для моделирования шинных структур в алфавит допустимых значений сигналов вводится ещё одно Z-состояние, то есть состояние высокого импеданса на выходе, когда он фактически оторван от нагрузки: {0,1,X,R,F,Z}. Весьма распространён четырёхзначный алфавит {0,1,X,Z}. Он используется в таких языках описания аппаратуры как Verilog, ABEL, AHDL (Altera), DSL (DesignLab). Четырёхзначный алфавит часто называют алфавитом синтеза ПЛИС.

Модели цифровых сигналов Для более точного представления сигналов (более адекватного моделирования) можно использовать два основных приёма: Расширять алфавит моделирования (так мы уже действовали); Вводить понятие логической силы сигнала (strength level). В качестве примера рассмотрим расширенный алфавит моделирования языка VHDL type bit is (0,1); - базовый, встроенный тип сигнала. Алфавит {0,1} type std_ulogic is (U,X,0,1,Z,W,L,H,-); - расширенный тип сигнала. Алфавит {U,X,0,1,Z,W,L,H,-} Расширенный тип сигналов расположен в отдельном пакете std_logic_1164, находящимся в библиотеке ieee. Поэтому чтобы включить этот тип сигналов в модель, необходимо перед ней разместить строки:

Модели цифровых сигналов Язык VHDL Алфавит {U,X,0,1,Z,W,L,H,-} U – от слова Uninitialized – дословно «не инициализировано» Это означает, что сигналу в программе вообще не присваивались какие- либо значения; обеспечивает контроль корректности инициализации - – безразличное состояние (Dont Care) Это означает, что сигнал может принять любое из разрешённых значений, что не повлияет на работу схемы. В книгах и справочниках безразличное состояние часто обозначают символами «d» или «*». JK-триггер R C J K Q NQ Сброс 1 * * * 0 1 При синтезе ЦА в запрещённых состояниях вместо «*» вы можете поставить 0 или 1 и получите разные схемные решения. В САПР выбор конкретного значения отдаётся на откуп компилятору с целью оптимизации проектируемого устройства. Пример. Язык DSL в САПР DesignLab 8. В выражении Y =.X.; компилятор по умолчанию PLSyn поставит Y = 0;

Модели цифровых сигналов Active-HDL 8.1 Графическое представление значений цифрового сигнала. Понятия сильного (force) и слабого (weak) сигналов X – forcing unknown 0 – forcing zero 1 – forcing one W – weak unknown L - weak zero (слабый ноль) H - weak one (слабая единица) Слабый сигнал формируется от источников, называемых драйверами. Они имеют высокое выходное сопротивление по сравнению с источниками сильных сигналов. Например, схема с открытым коллектором или эмиттером.

Модели цифровых сигналов SDRZ 0S0D0R0Z0 1S1D1R1Z1 XSXDXRXZX Вернёмся к понятию логической силы сигнала (strength level). Мы уже знаем, что расширение возможностей моделирования, повышения его адекватности, может достигаться не только увеличением алфавита моделирования, но и введением понятия «уровня логической силы сигнала». Впервые эта идея была реализована в языке PML пакета PCAD 4.5. Пример: Язык Verilog имеет всего 4х-значный алфавит моделирования {0,1,X,Z}, но одновременно 8 значений логической силы. Логическая сила S > D > R > Z

D > R > Z">

Модели логических элементов При построении моделей логических элементов могут учитываться следующие свойства: выполняемая функция; задержка распространения сигнала; нагрузочная способность; пороги срабатывания; длительность фронтов; случайный разброс задержек; температурные изменения параметров (например, временных задержек, уровней логического нуля и единицы и т.п.). Заметим, что чем выше значимость алфавита моделирования и чем больше свойств учитывается в модели, тем больше ресурсов (процессорного времени и памяти) требуется для прогона модели. По этой причине в современных системах моделирования число разрешённых значений цифрового сигнала обычно не превышает 4..9, а из возможных свойств, как правило, моделируется только функция, временная задержка и нагрузочная способность.

Булевские модели Булевские модели логических элементов работают с двоичным алфавитом {0,1} и могут быть реализованы в виде: логического уравнения, таблицы истинности или блок-схемы алгоритма IN1 IN2 OUT1 & AND2 IN1 IN2 OUT1 & AND2 IN1 IN2 OUT1 & AND2 F1 F2 Y1 Потоковое описание схемы: Y1 = A & B; (PCAD 4.5, язык PML) Y1 = A * B; (DesignLab 8, язык DSL) Y1

PROCEDURE AND2 (INPUT IN1, IN2 ; OUTPUT OUT1); TRUTH_TABLE IN2, IN1:: OUT1; 1, 1:: 1; END TRUTH_TABLE; END AND2; Булевские модели IN1 IN2 OUT1 & AND2 IN1 IN2 OUT1 & AND2 IN1 IN2 OUT1 & AND2 F1 F2 Y1 IN1IN2OUT Алгоритмическое описание Табличное описание Язык DSL Начало Конец IN1=0 IN2=0 OUT1=0OUT1=1 Да Нет Да Нет

Булевские модели Обычно булевские модели применяются для синхронного потактового моделирования (принцип дельта Т) без учёта задержек. Это самое примитивное моделирование. Главное его достоинство – простота и экономичность. При булевском моделировании время разбивается на такты (принцип t). Длительность такта выбирается так, чтобы в пределах одного такта ни один сигнал не переключился более одного раза. Реальное переключение переносится на начало того такта, в пределах которого оно произошло. Переключение считается мгновенным. Задержка распространения сигнала от входа F1 (или F2) до выхода Y1 не моделируется, так как оба переключения переносятся на начало такта Т2 (или Т4) и становятся одновременными. Модельное время F1 F2 Y1 Такт Реальный сигнал Булевская модель T0T1 T2 T3T4T5T6 Риск сбоя Мгновенное событие «Иголка» Glitch

Булевские модели Обычно один такт соответствует одному набору входных сигналов и обрабатывается за один цикл работы моделятора. С каждым циклом в счётчик модельного времени добавляется единица, то есть модельное время продвигается по тактам в соответствии с выражением: Т:=Т+1. В реальной схеме из-за перекрытия фронтов сигналов F1 и F2 на выходе элемента 2И может появиться короткий импульс - риск сбоя (такт Т6). Булевские модели не в состоянии предсказать появление таких иголок, весьма опасных для работы цифровой аппаратуры. Булевское моделирование решает только одну главную задачу любого моделирования – проверку правильности функционирования цифровой аппаратуры

Троичные модели Троичные модели в отличие от булевских имитируют возникновение переходных процессов при смене уровней сигналов. При троичном моделировании такт разбивается на два полутакта. В течение первого полутакта переключающийся сигнал принимает значение Х (изменяется), а на втором полутакте достигает нового значения. В троичных моделях используется трёхзначный алфавит {0,1,X}

Троичные модели Модельное время F1 F2 Y1 Реальный сигнал Риск сбоя 0 1 X Модель риска сбоя Троичная модель 1 X X Такт T6 Полутакт неопределённости Полутакт определённости IN1 IN2 OUT1 & AND2 IN1 IN2 OUT1 & AND2 IN1 IN2 OUT1 & AND2 F1 F2 Y1 IN1IN2OUT IN1IN2OUT1 0X0 X00 1XX X1X XXX M2 M3 1X0 0X1 0X0 таблица истинности элемента 2И для трёхзначной логики

Троичные модели Признаком риска сбоя служат одинаковые значения сигнала на соседних тактах и значение Х на полутакте неопределенности между ними. 0011XX Риск сбоя Троичное моделирование отражает только сам факт переключения сигнала и не уточняет, сколько времени длилось переключение, и где именно в пределах такта оно происходило. Другими словами, длительность Х - состояния при троичном моделировании всегда равна полутакту и никак не связана с реальным временем переключения сигнала.

Многозначные модели Многозначные модели позволяют более точно описать поведение реальных элементов, однако по сравнению с троичными моделями ничего принципиально нового они не содержат. Для сравнения рассмотрим таблицы истинности элемента 2И при двоичном, троичном и пятизначном моделировании. OUT1 IN2 01X IN X X0XXXX 0 X X 0 XX IN1 IN2 OUT1 & AND2 IN1 IN2 OUT1 & AND2 IN1 IN2 OUT1 & AND2 F1 F2 Y1 X ? IN1 IN2 OUT1 & AND2 ? IN1 IN2 OUT1 & AND2 M2M3 M5

Модели логических элементов с учётом задержек Эти модели в отличие от троичных имитируют задержки в явном виде. Чтобы отобразить задержку, надо указать истинное положение переключающегося сигнала на временной оси. Моделирование задержек при потактовом способе продвижения модельного времени (принцип дельта T). Чтобы отразить задержку, надо повысить разрешающую способность по времени, то есть разделить такт на более мелкие единицы времени, называемые квантами (микротактами) или шагами. Например, в пакете PCAD такт называется CYCLE, а квант - STEP. 1 A Y A Y Квант Такт tз = 8 квантов Задержка представляется целым числом – числом квантов

Модели логических элементов с учётом задержек В моделях с учётом tз в явном виде такт нарезается на кванты. Причем величина кванта должна составлять малую часть задержки, например 1ns. Цикл работы моделирующей программы теперь привязывается не к такту, а к кванту. Поэтому, чтобы смоделировать работу схемы в течение одного такта, моделятору придётся выполнить гораздо больший объём работы, а именно столько циклов, сколько квантов помещается на длине такта. Теперь с точностью до кванта можно указать моменты истинных переключений на входах и выходах, а также вычислить целым числом квантов задержку распространения. Остается только смоделировать её. Классическая модель логического элемента с учётом задержки содержит два блока. Первый – реализует логику (функцию), второй – чистую задержку. φ tз = 0 B A C YсYс Y Логический блок Блок задержки Yс (от слова синхронный) мгновенно реагирует на изменения входных сигналов Динамическая модель в PSpice проектах

Модели логических элементов с учётом задержек AYсYс Логический блок LOGICEXP PINDLY Счётчик tз Контейнер Yс Контейнер Y Y NextCurrent Хранит будущее значение Хранит текущее значение Блок задержки Возможная реализация блока задержки для потактового моделирования Счётчик задержки работает на вычитание. При синхронном переключении выхода Yс новое значение записывается в контейнер будущих значений, а в счётчик tз заносится задержка, с которой новое значение Yс должно появиться на выходе Y.

Модели логических элементов с учётом задержек В процессе продвижения модельного времени (tкванта = tкванта + 1) задержка в счётчике tз уменьшается, по не «растает» до нуля. Будущее значение выхода становится текущим, а это означает, что содержимое левого контейнера надо переписать в правый. Моделирование задержек при событийном механизме продвижения модельного времени (принцип дельта Z). Мы рассмотрели вариант, когда задержка моделируется внутри каждого логического элемента. Такое решение приводит к значительным затратам ресурсов инструментальной ЭВМ. Другая возможность смоделировать реальную задержку заключается в том, чтобы спланировать новое событие на выходе и рассчитать момент его наступления t(Y) по простому правилу: t(Y) = t(Yс) + tз Но t(Yс) – это текущее модельное время t(текущее) Значит для любого события (переключения) можно спланировать время наступления будущего события как t(будущее) = t(текущее) + t(задержки)

Модели логических элементов с учётом задержек Вычисленное событие помещается моделятором в очередь будущих событий ОБС, которая отсортирована в хронологическом порядке. Как видно, вся работа по имитации задержек перекладывается на моделятор, которому требуется только указать величину задержки относительно текущего модельного времени. Заметим, что округлять ее до целого числа квантов теперь совсем не обязательно. На языке VHDL это делается весьма элегантно: Y

Цифровое моделирование на современном этапе развивается наиболее динамично. Это связано с интенсивным развитием математического обеспечения, формирующегося в виде пакетов прикладных программ. Использование этих пакетов повышает производительность моделирования и одновременно упрощает его.

Достоинства метода цифрового моделирования:

1. Решается любой класс задач подлежащих математической интерпретации;

2. Высокая точность решения (ограничена только временем решения задачи);

3. Легкость перехода от одной задачи к другой (необходимо лишь перезапустить программу);

4. Возможность исследования объектов высокой размерности.

Недостаток метода цифрового моделирования – конечное время моделирования, которое может не совпадать с реальным временем.

Цифровая вычислительная машина - это комплекс технических устройств, в которых могут протекать процессы, отображающие (моделирующие) действия с числами. Именно действия над числами составляют суть вычислительных операций при численном решении различных математических задач. Моделирование процесса численного решения математической задачи на ЦВМ практически означает автоматическое решение ее с помощью ЦВМ.

Числа могут не только выражать значение постоянных и переменных величин, но и являться символическими условными моделями самых разнообразных других объектов - букв, слов, предметов, явлений и т.д. Это позволяет свести к действиям над числами различные невычислительные задачи, например, определение числа объектов с заданными свойствами. Благодаря этому возможно моделирование на ЦВМ процедуры решения невычислительной задачи, т.е. машинная реализация этого решения.

Процесс функционирования любого материального объекта представляет последовательную смену его состояний во времени, каждое из которых определяют конкретные значения некоторых физических величин. Если объект является непрерывной системой, то эти величины - непрерывные функции непрерывного времени.

Математическое описание объекта составляют различные математические формы выражения количественных соотношений между переменными и постоянными. Это различные функции, уравнения, системы уравнений, условия однозначности их решений, неравенства и другие математические представления.

Если известно математическое описание функционирования объекта-оригинала, согласно этому описанию определен процесс над числами, выражающими значения величин, характеризующих состояние объекта, и этот процесс отображен в ЦВМ, то процесс, реализуемый ЦВМ, является материальной функциональной формальной математической подобной цифровой моделью оригинала.

Дискретная природа функционирования ЦВМ требует, как правило, приведение исходного математического описания оригинала к виду, удобному для цифрового моделирования. Прежде всего необходима дискретизация непрерывных величин. При этом непрерывные функции подвергаются квантованию по уровню и аргументу. В результате непрерывная функция непрерывного аргумента y = f(t) превращается в дискретную функцию дискретного аргумента

T y k y = f (Tk),

где k и k y - числа принимающие значения 0, ± 1, ± 2, ± 3, ... ; T и Ty - кванты переменных t и y.

Квантование по уровню - это замена значения y соответствующим числом определенной разрядности, сопровождающаяся погрешностью округления

D y < T y /2.

Поскольку в современных ЦВМ число разрядов велико 32 и более и погрешность пренебрежимо мала, поэтому практически можно считать, что функционирование ЦВМ описывается решетчатыми функциями вида

y = f (Tk) = f [ k ]

и моделирует их.

Для цифрового моделирование оригинала необходима алгоритмизация математического описания оригинала. Алгоритм - это точно определенное правило выполнения расчетных операций над числами, последовательность которых составляет общий процесс преобразования исходных данных в результат решения соответствующей задачи. Алгоритмизация математического описания заключается в получении соответствующего этому описанию алгоритма. Если, например, функционирование оригинала описывается дифференциальным уравнением, то алгоритмизация заключается в составлении алгоритма численного решения этого уравнения. По существу алгоритмизация математического описания и заключается в приведении его к виду, удобному для цифрового моделирования. Она выполняется на основе выбранного численного метода решения задачи, который позволяет свести решение к арифметическим действиям. При этом часто оказывается полезным применение аппарата решетчатых функций

Алгоритм может быть представлен в трех основных формах: аналитической, словесной и структурной.

Аналитическая форма алгоритма - это выражение его в виде явной функции соответствующих аргументов или в виде рекуррентной формулы. Форма отличается большой компактностью, но возможности применения ее ограничены.

Словесная форма алгоритма - это его описание его на естественном языке, обстоятельная инструкция для лица, решающего задачу вручную на бумаге. Форма является универсальной, но отличается громоздкостью и отсутствием наглядности.

Структурная форма алгоритма - это его описание в виде структурной схемы, состоящей из отдельных блоков, соединенных прямыми линиями. Каждый блок соответствует некоторой операцией над числами. Форма является универсальной, компактной и наглядной. Поэтому она используется наиболее часто.

В целом процесс моделирования на ЦВМ состоит из следующих этапов:

1. Составление исходного алгоритма, т.е. алгоритмизация математического описания оригинала.

2. Составление промежуточного алгоритма на алгоритмическом языке.

3. Получение машинного алгоритма.

4. Отладка программы.

5. Машинная реализация решения задачи.

Первые четыре подготовительных этапа значительно упрощаются благодаря применению типовых алгоритмов и соответствующих им стандартных программ, заранее составленных и многократно используемых для решения таких задач, как вычисление элементарных функций, определение нулей полиномов, перевод чисел из одной системы счисления в другую и др.

Комплекс программных средств, предназначенных для снижения трудоемкости подготовительной работы, повышения эффективности использования машины и облегчения ее эксплуатации, называется математическим обеспечением ЦВМ.

При цифровом моделировании наиболее часто приходится иметь дело с решетчатыми функциями f[k], соответствующими непрерывным функциям непрерывного аргумента. Непрерывная функция, совпадающая с дискретами решетчатой функции, называется огибающей этой решетчатой функции. Каждая непрерывная функция f(t) может служить огибающей различных решетчатых функций f i [k] = f(T i k), отличающихся параметром T i - периодом дискретизации функции f(t). Каждая решетчатая функция может иметь множество различных огибающих.

Различным математическим формам и представлениям, характеризующим или определяющим непрерывную функцию f(t), можно поставить в соответствие аналоги, характеризующие или определяющие решетчатую функцию f(k). Аналогом первой производной функции f(t)

являются первое разностное уравнение функции f[k]

Т.е. совершается переход к численным методам решения.

Итак, окончательно,

* первым этапом является при проектировании является выбор наиболее подходящей математической модели. Этот этап должен обеспечить получение наиболее удачной математической модели и выработке требований к условиям модели;

* вторым этапом процесса проектирования является подготовка математической модели для моделирования. Задача решается приведением к структурной схеме дискретного процесса и приведением системы уравнений к дискретной форме. Этот этап завершается двумя результатами: математическим описанием и структурной схемой всей дискретной системы. Структурная схема полученной дискретной системы должна быть идентична структурной схеме непрерывной системы по потоку информации;

* третьим этапом является написание программы для осуществления математического моделирования. Это решающий этап, содержащий строгое соблюдение временных соотношений в синтезируемой математической модели, как правило наибольшее число проблем возникает при переходе от задач 2го этапа к задачам 3го этапа;

* четвертый этап испытание, проверка и отладка модели, после которого получается законченная модель.

2.2. Неалгоритмические методы

цифрового моделирования.

Скорость решения ряда сложных задач программно-алгоритмическим методом на ЦВМ общего назначения недостаточна и не удовлетворяет потребностям инжененрных систем автоматизированного проектирования (САПР). Одним из таких классов задач, широко применяемых в инженерной практике при исследовании динамики (переходных процессов) сложных систем автоматизации, являются системы нелинейных дифференциальных уравнений высоких порядков в обыкновенных производных. Для ускорения решения названных задач в состав программно-технических комплексов САПР могут включаться в дополнение к главной (ведущей) ЦВМ общего назначения ГВМ, проблемно-ориентированные на решение нелинейных дифференциальных уравнений. Они организуются на основе цифрового математического моделирования неалгоритмическим методом. Последний позволяет повысить производительность САПР за счет присущего ему параллелизма вычислительного процесса, а дискретный (цифровой) способ представления математических величин – достичь точности обработки не хуже, чем в ЦВМ. В этих ГВМ применяются два метода цифрового моделирования:

1. Конечно-разностное моделирование;

2. Разрядное моделирование.

Первый метод, используемый в ГВМ типа цифровых дифференциальных анализаторов (ЦДА) и цифровых интегрирующих машин (ЦИМ), – это известный метод приближенных (пошаговых) вычислений в конечных разностях. Цифровые операционные блоки ГВМ, построенные на цифровой схемотехнике, обрабатывают достаточно малые дискретные приращения математических величин, передаваемые по линиям связи между операционными блоками. Вводимые и выводимые математические величины представляются, хранятся и накапливаются из приращений в цифровых n-разрядных кодах в риверсивных счетчиках или регистрах накапливающих сумматоров.

Приращения всех величин обычно кодируются одной единицей младшего разряда: D:=1мл. р. Это соответствует квантованию по уровню всех обрабатываемых величин с постоянным шагом квантования D=1. Следовательно, ограничивается скорость нарастания всех машинных величин: |dS/dx|£1.

Знаки одноразрядных приращений кодируются методом знакового кодирования на двухпроводных линиях связи между операционными блоками:

https://pandia.ru/text/78/244/images/image002_51.gif" width="476" height="64 src=">,

где DSi=yiDx – приращение интеграла в i-м шаге интегрирования, а i-я ордината подинтегральной функции y(x) – yi вычисляется путем накопления её приращений:

https://pandia.ru/text/78/244/images/image004_39.gif" width="208" height="56 src=">

с введением постоянного нормирующего коэффициента кн = 2-n приращения на выходах интеграторов образуются последовательно и обрабатываются в следующих интеграторах также последовательно. Исключением является интегрирование суммы нескольких подинтегральных функций

https://pandia.ru/text/78/244/images/image006_34.gif" width="239" height="56 src=">

Тогда по нескольким m входным линиям l-е приращения могут поступать синхронно в каком-то j-м шаге. Для последовательного сложения их разносят в пределах шага с помощью линий задержек, увеличивая в m раз тактовую частоту работы входного накапливающего сумматора. Поэтому число суммируемых подинтегральных функций обычно ограничивают до двух.: m=2.

Структурная организация цифрового интегратора-сумматора весьма проста. Он строится в виде последовательного соединения следующих функциональных узлов:

· схема 2ИЛИ с линией задержки tз=0,5t на одном из входов

· входной накапливающий сумматор приращений подинтегральных функций, выполняющий накопление n-разрядных их ординат по входным приращениям:

https://pandia.ru/text/78/244/images/image008_28.gif" width="411" height="194 src=">

При Dх:=(10) код yk передается без изменений, а при Dх:=(01) на выходе образует код, обратный входному коду yk.

Выходной накапливающий сумматор, который в каждом к-ом шаге интенрирования прибавляет к своему старому содержимому содержание регистра сдвига РС входного НСМ (в последовательном коде передачи этот шаг выполняется за n тактов):

· формирователь выходного приращения интеграла: DSi:= единица переполнения Si, преобразующий признак переполнения в биполярный код приращения (наиболее просто он реализуется, если отрицательные накопленные числа Si представить в модифицированном коде: прямом, обратном или дополнительном). Соответствующая структурная схема цифрового интегратора приведена на рис. 9.14 (с.260) учебника . В схемах цифровых моделей применяется следующее условное обозначение цифрового сумматора-интегратора:

«Зн.» указывает признак инверсии (-), если она требуется. Важным преимуществом данного метода конечно-разностного цифрового моделирования является то, что один и тот же цифровой интегратор без изменения его схем используется для выполнения линейных и нелинейных операций, необходимых для решения обыкновенных дифференциальных уравнений. Это объясняется тем, что при программировании ЦДА и ЦИМ исходные уравнения в производных преобразуются к уравнениям в дифференциалах. Рассмотрим простейшие программы цифровых моделей:

1. умножение переменной х на константу к:

Перейдя к дифференциалам dS=кdx, убедимся в том, что эта операция выполняется одним интегратором при соответствующей его начальной установке:

3. Умножение S=xy, или в дифференциалах dS=xdy+ydx.

4.2. тригонометрические функции, например y=sinx, которая является решением дифференциального уравнения второго порядка (так как ), или в дифференциалах

|

DIV_ADBLOCK93">

Учитывая то, что создание названных проблемно-ориентированных ГВМ требует существенных дополнительных затрат, при построении технических средств САПР чаще используется более простой способ их организации путем объединения в вычислительный комплекс серийно производимых ЦВМ общего назначения и электронных аналоговых вычислительных машин (АВМ), построенных на операционных усилителях. ЦВМ и АВМ объединяются с помощью типового устройства преобразования и сопряжения (УПС), состоящего в основном из АЦП и ЦАП. Сложная решаемая задача рационально распределяется на 2 части между аналоговыми и цифровыми процессорами при программировании комплекса. Причем аналоговая часть чаще всего проблемно ориентируется на решение дифференциальных уравнений и используется в общем вычислительном процессе как быстрая подпрограмма.

2.3 Архитектура гибридных вычислительных комплексов (ГВК).

2.3.1. структура аналого-цифрового вычислительного комплекса (АЦВК)

ГВК или АЦВК – это вычислительный комплекс, состоящий из ЦВМ и АВМ общего назначения, объединенных с помощью УПС, и содержащей в цифровой части дополнительное программное обеспечение для автоматизации программирования аналоговой части, управления обменом информацией между аналоговой и цифровой частями, конотроля и тестирования аналоговой части, автоматизации процедур ввода-вывода.

Рассмотрим структурную схему АЦВК с простейшим УПС, построенном на одноканальных коммутируемых АЦП и ЦАП. Для создания предпосылок автоматизации программирования АВМ под управлением ЦВМ в составе технических средств АВМ вводятся следующие дополнительные блоки:

1. Вручную регулируемые переменные сопротивления (потенциометры) на входах операционных усилителей в наборе операционных блоков (НОБ), известные Вам из лабораторных работ по ТАУ, заменяются на цифроуправляемые сопротивления (ЦУС), в качестве которых используются интегральные схемы ЦАП;

|

Для долговременного хранения кодов настройки ЦУС применяется блок буферных регистров (БФР), загружаемых при программировании АВМ цифровыми кодами коэффициентов передачи (КП) операционных блоков, вычисляемыми в ЦВМ по методике, изложенной в пункте 2.1; используя масштабные уравнения аналоговой модели;

3. Автоматическое соединение операционных блоков в соответствии с составленной в ЦВМ схемой аналоговой модели (п. 2.1) осуществляется схемой автоматической коммутации (САК) по двоичному вектору коммутации ключей САК, образованному в ЦВМ и хранящемуся в течении решения задачи в регистре настроечной информации (РН) в УПС.

Режимы работы АВМ: подготовка, пуск, останов, возврат в начальное состояние, вывод резудьтатов на аналоговые периферийные устройства (самописцы, двухкоординатные планшетные регистрирующие приборы – ДРП) задаются со стороны ЦВМ через блок управления УПС (БУ УПС).

БУ УПС осуществляет также взаимную синхронизацию работы ЦВМ и АВМ: передает сигналы внешнего прерывания из аналоговой модели в цифровые программы ЦВМ, под управлением программ цифровой части синхронизует опрос точек в аналоговой модели, преобразование напряжений в этих точках в цифровые коды и передачу последних через БСК и канал ввода–вывода в оператиыную память ЦВМ; или аналогично обратное преобразование цифровых кодов в электрические напряжения и подачу последних в требуемые точки на входы операционных блоков аналоговой модели. Такой принцип функциональной организации взаимодействия цифровой и аналоговой частей аппаратно поддерживаемо блоками УПС: АЦП и ЦАП, АМ и АДМ – аналоговыми мультиплексором и демультиплексором, МЛ – входным и выходным блоками аналоговой памяти, построенными на множестве однотипных схем выборки хранения (СВХ). Входы входных СВХ (слева) подключаются к требуемым точкам схемы аналоговой модели (выходам соответствующих операционных блоков). В необходимые дискретные моменты времени под управлением ЦВМ с аналоговой модели снимаются отдельные выборочные ординаты аналоговых сигналов (электрических напряжений) и запоминаются в СВХ. Затем выходы СВХ опрашиваются мультиплексором АМ и их выходные напряжения преобразуются в АЦП в цифровые коды, которые в режиме прямого доступа как блок чисел (линейный массив) записываются в ОП ЦВМ.

При обратном преобразовании выходы СВХ второй группы выходной аналоговой памяти МЛ (справа) подключаются под управлением ЦВМ к требуемым входам операционных блоков аналоговой модели, а входы СВХ – к выходам аналогового демультиплексора, на вход которого подается выходное напряжение ЦАП. В режиме прямого доступа из ОП ЦВМ считывается блок чисел. Каждое из чисел преобразуется в ЦАП в электрическое напряжение, которое под управлением ЦВМ с помощью обегающего АДМ записывается на хранение в одну из СВХ. Полученный набор нескольких напряжений хранится в нескольких СВХ в течение заданного по программе ЦВМ интервала времени (например, во время решения задачи в аналоговой части) и обрабатывается аналоговыми операционными блоками.

2.3.2. Методы организации аналого –

цифровых вычислений.

Принцип чередования режимов работы ЦВМ и АВМ, снижающий сложность УПС.

АЦВК применяются для аналого – цифрового моделирования сложгых систем автоматизации, содержащих управляющие ЦВМ, а также для ускорения решения сложных математических задач, требующих чрезмерного расхода ресурсов памяти и машинного времени ЦВМ. В первом случае на ЦВМ программно имитируются алгоритмы управления, а в АВМ программируется аналоговая математическая модель объекта управления, и АЦВК используется как комплекс для отладки и верификации алгоритмов управления с учетом нелинейности и динамики объекта управления, которые очень трудно учесть при разработке алгоритмов, если при этом постоянно не решать дифференциальные уравнения объекта для определения его реакции на каждое новое управляющее воздействие.

Во втором случае, например, при решении дифференциальных уравнений, общую громоздкую задачу приближенных вычислений разбивают на две части, помещая обычно в аналоговую часть вычислительно емкие расчеты для которых допустима погрешность 0.1…1%.

По принципу названного разделения задачи на две части и способу организации взаимодействия между АВМ и ЦВМ современные АЦВК подразделяются по 4 классам аналого–цифровых вычислений

Классы 1,2,3 могут быть реализованы на основе рассмотренной структурной организации АЦВК с упрощенным УПС, построенном наодноканальных АЦП и ЦАП.

Класс 1 наиболее простой по организации взаимодействия между АВМ и ЦВМ. Цифровая и аналоговая части работают в разное время, и поэтому не предъявляется высоких требований к синхронизации работы АВМ и ЦВМ и быстродействию ЦВМ и УПС.

Класс 2 требует особой организации чередования режимов работы АВМ, ЦВМ и УПС в каждом цикле вычислений и взаимодействия

Вычисление | |||||

Передача данных | Передача данных | ||||

Прерывание | Вычисление | Прерывание | Вычисление |

Так как АЧ и ЦЧ одновременно не работают, нет проблем с их синхронизацией и не предъявляется высоких требований к быстродействию УПС и ЦВМ. Классы решаемых задач: оптимизация параметров аналоговой модели, параметрическая идентификация, моделирование случайных процессов методом Монте–Карло, аналого–цифровое моделирование САУ не в реальном масштабе времени, интегральные уравнения.

Класс 3 требует другой организации чередования режимов работы АВМ, ЦВМ и УПС.

Вычисление | |||||

Передача данных | Передача данных | ||||

Вычисление | Прерывание | Вычисление | Прерывание |

В фазе А в АЧ и ЦЧ одновременно выполняются 2 частные задачи одной сложной задачи, совместимые по времени. В ЦЧ в фазе В чаще всего принимаются из АЧ и запоминаются дискретные величины аргументов функций, затем в фазе А по ним вычисляются, заготавливаются для АЧ, ординаты сложных функций, которые в следующей фазе В передаются в АЧ, где заносятся на хранение в аналоговые ЗУ (СВХ), а затем используются в следующей фазе А в аналоговых вычислениях, и т. д. Классы решаемых задач: итеративные вычисления, решение обыкновенных дифуров с заданными граничными условиями, динамических задач с чистым запаздыванием аргументов, интегральных уравнений, дифференциальных уравнений в частных производных. В классе 3 не предъявляется высоких ьребований к быстродействию ЦВМ и УПС, но требуется точная синхронизация работы АВМ и ЦВМ в фазе В, так как из–за останова цифрового процессора асинхронное управление передачи данных невозможно, а осуществляется синхронная передача блоков данных под управление контроллера прямого доступа в память (КПДП) через канал ввода–вывода ЦВМ.

Класс 4 – это чаще всего аналого–цифровое моделирование цифровых САУ в реальном масштабе времени для проверки и отладки программ управляющей ЦВМ в динамике. Он наиболее сложен по организации взаимодействия и синхронизации работы АВМ и ЦВМ, тпк как здесь фазы А и В совмещены, происходит постоянный взаимный обмен данными в процессе вычислений, и поэтому требуется применение ЦВМ и УПС максимального быстродействия.

Структурная организация УПС, приведенная выше и пригодная для классов 1,2,3, в классе 4 неприменима. В последнем классе требуется многоканальная организация АЦП и ЦАП без мультиплексирования с дополнительным включением на входе м выходе БСК файла параллельных буферных регистров, обменивающихся с ОП ЦВМ в режиме прямого доступа. Содержимые каждого из регистров либо преобразуются отдельными параллельно включенными ЦАП при передаче данных в АВМ, либо формируются отдельными параллельно включенными АЦП при передаче данных из АВМ в ЦВМ.

2.3.3 Особенности программного обеспечения АЦВК.

Для автоматизации программирования АВМ с помощью ЦВМ и полной автоматизации аналого–цифрового вычислительного процесса традиционное ПО ЦВМ общего назначения (см. рис. 13.2 с.398 в учебнике ) дополняется следующими программными модулями:

1. В состав обрабатывающих программ входят дополнительные трансляторы со специальных языков аналого–цифрового моделирования, например Фортран-IV, дополненного подпрограммами на расширенном Ассемблере, содержащем специальные аналого–цифровые команды, например, для управления аналоговой частью по программе ЦВМ, организации передачи данных между ЦЧ и АЧ, обработки прерываний программ ЦЧ, инициализируемых аналоговой частью; создается аналого–цифровая компилирующая система;

2. В состав рабочих, отладочных и обслуживающих программ вводят драйвер межмашинного обмена для управления аналоговой частью как периферийным процессором, программы графического дисплея, регистрации и анализа результатов;

3. В состав библиотеки прикладных программ вводят программы вычисления функций и стандартные математические аналого–цифровые программы;

4. В состав диагностических программ технического обслуживания вводят тесты УПС, тесты операционных блоков АВМ;

5. В состав управляющих программ ОС вводят целый комплекс дополнительных управляющих модулей:

· Система автоматизации аналогового программирования (СААП), состоящая из лексического анализатора ; синтаксического анализатора (проверка соответствия введенной на алгоритмическом языке аналоговой программы правилам синтаксиса записи); генераторы структурных схем (составление и кодирование схем аналоговых моделей методом понижения порядка и неявных функций также, как и в п.2.1); блока расчетных программ (масштабирование аналоговой модели как в п.2.1, цифровое программное моделирование аналоговой части на ЦВМ с однократным просчетом для расчета ожидаемых максимальных значений переменных и уточнения масштабирования аналоговой модели, а также создание файла статического и динамического контроля аналоговой части после её программирования); программы представления выходной информации (вывод на дисплей и графопостроитель синтезированной структуры аналоговой модели, контрольная распечатка кодов аналоговой программы, масштабных коэффициентов, файла статического и динамического контроля);

· Служба синхронизации и взаимодействия АВМ и ЦВМ (реализация чередования режимов работы);

· Служба обработки прерываний, инициализируемых аналоговой частью;

· Программа управления обменом данными между АВМ и ЦВМ;

· Программа управления загрузкой кодов схемы аналоговой модели в САК (в РН);

· Программа управления режимом статического и динамического контроля (отладка загруженной в АВМ аналоговой программы).

По результатм автоматизации аналого–цифрового программирования на магнитном диске ведущей ЦВМ, кроме традиционных цифровых файлов, создаются следующие дополнительные файлы данных, используемые названными выше дополнительными модулями ПО АЦВК: файл аналоговых блоков, файл коммутации (для САК), файл статического контроля, файл динамического контроля, файл подготовки аналоговых функциональных преобразователей, библиотека подключаемых стандартных аналого–цифровых программ.

2.3.4. Языки аналого–цифрового моделирования.

Рассмотренная архитектура АЦВК позволяет описывать и вводить аналого–цифровые программы только в ведущую ЦВМ на алгоритмических языках высокого уровня. Для этого традиционные языки цифрового программирования дополняются специальными операторами описания объекта аналогового моделирования, организации передачи данных между АЧ и ЦЧ, управления аналоговой частью по программе ЦВМ, обработки прерываний со стороны аналоговой части, задание параметров аналоговой модели, контроля аналоговой части, задания служебной информации и т. п.

Применяются универсальные языки, транслируемые путем компиляции (Фортран IV) или интерпретации (Бейсик, Гибас, Фокал, HOI), дополняемые специальными подпрограммами на Ассемблере, обычно выызваемыми оператором Call… с указанием идентификатора нужной подпрограммы.

С целью повышения скорости работы СААП она обычно описывается и использует на входе специализированные языки аналого–цифрового моделирования: CSSL, HLS, SL – 1, APSE, а для внутренней интерпретации язык Полиз (обратная польская запись).

В универсальные языки компилируемого типа могут вводиться следующие аналого–цифровые макрокоманды:

1. SPOT AA x – установить потенциометр (ЦУС) в аналоговой части с адресом АА в положение (величину сопротивления), соответствующее значению цифрового кода, хранящемуся в ОП ЦВМ по адресу х;

2. MLWJ AA x – считать аналоговую величину на выходе операционного блока в АЧ с адресом АА, подвергнуть её аналого–цифровому преобразованию, а результирующий цифровой код записать в ОП ЦВМ по адресу х. Взаимодействие аналоговой частии цифровой части можно описать как вызов процедуры:

Call JSDA AA x, где JSDA – это идентификатор соответствующий, подключаемой подпрограммы на Ассемблере, например, процедуры установки – установить значение х с выхода ЦАП по адресу АА в аналоговой части.

Поэтому очень важно понять как тип параллелизма решаемой задачи влияет на способ оргпнизации параллельной ЭВМ.

3.1.1 Естественный параллелизм

независимых задач.

Он наблюдается, если в ВС поток не связанных между собой задач. В этом случае повышение производительности сравнительно легко достигается путем введения в «крупнозернистую» ВС ансамбля независимо функционирующих процессоров, подключенных к интерфейсам многомодульной ОП и инициализации процессоров ввода/вывода (ПВВ).

Число модулей ОП m>n+p c тем, чтобы обеспечить возможность параллельного обращения в памятьвсех обрабатывающих процессоров и всех ПВВ и повысить отказоустойчивость ВС. Резервные (m-n-p) модули ОП необходимы для быстрого восстановления при отказе рабочего модуля и для хранения в них ССП процессоров и процессов в контрольных точках программ, необходимых для рестарта при отказе процессора или модуля ОП.

Создается возможность под каждую из решаемых задач временно объединять пару: Пi+ОПj как автономно функционирующую ЭВМ. Предварительно этот же модуль ОП работал в паре: ПВВк+ОПj, и в ОПj в буфер ввода была занесена программа и данные. По окончании обработки в ОПj организуется и заполняется буфер вывода, а затем модуль ОПj вводится в пару ОПj+ПВВr для обмена с периферийным устройством.

Основная задача организации вычислительных процессов, решаемая системной программой «диспетчер», – оптимальное распределение задач между параллельными процессорами по критерию максимальной их загрузки, или минимизации времени их простоев. В этом смысле оптимальным является асинхронный принцип загрузкм задач в процессоры, не ожидая, пока закончится обработка задач в других занятых процессорах.

Если пакет входных задач, накопленный за определенный интервал времени, хранится в ВЗУ, проблема оптимальной асинхронной диспетчирезации сводится к составлению оптимального расписания моментов запуска задач на разных процессорах. Основные исходные данные, требуемые для этого, – множество известных ожидаемых времен счета, процессорной обработки всех задач накопленного пакета, которые обычно указываются в управляющих картах их заданий.

Несмотря на независимый характер задач в совокупности их асинхронных вычислительных процессов возможны конфликты между ними за общие ресурсы ВС:

1) Услуги общей мультисистемной ОС, например обработка прерываний по вводу-выводу, или обращений к общей ОС надежности при отказах и рестартах;

(О–) – ®О-Д – изменение знака D.

При операции в I слое и по две операции во II и III слоях могли бы выполняться параллельно, если бы в составе АЛУ имелся соответствующий избыток операционных блоков.

Рассмотренный выше параллелизм операций в решении дифференциальных уравнений и при обработке матриц относится к классу регулярного, так как там одна и та же операция многократно повторяется над разными данными. Последний пример квадратного уравнения имеет нерегулярный параллелизм операций, когда над разными данными возможно одновременное выполнение разных типов операций.

Как показано выше, для использования регулярного параллелизма операций при повышении производительности подходит матричная организация ВС с общим управлением.

В общем случае нерегулярного параллелизма операций более подходящим способом повышения производительности считается потоковая организация ЭВМ и ВС. В потоковых ВС вместо традиционного фон Неймановского программного управления вычислительным процессом в соответствии с порядком следования команд, определяемого алгоритмом, применяется обратный принцип программного управления по степени готовности операндов, или потоком данных (потоком операндов), определяемой не алгоритмом, а графом операндов (графом передачи данных).

Если в параллельном процессоре имеется достаточный избыток обрабатывающих устройств, или в ВС – ансамбль избыточных микропроцессоров, то естественно и автоматически (без специальной диспетчирезации и составления расписания запуска) будут одновременно выполняться те параллельные операции, операнды которых подготовлены предыдущими вычислениями.

Вычислительный процесс начинается с тех операций, операндами которых являются исходные данные, как, например, в I слое ГПД квадратного уравнения одновременно выполняются три операции, а далее он развивается по мере готовности операндов. Послеэтого вызывается команда умножения, затем вычитания и проверки логического условия, потом макрооператор(Ö) и лишь после этого – одновременно две команды: сложения и вычитания, а после них – две одинаковых команды деления.

Техническая реализация потоковой организации ВС возможна тремя путями:

1) Созданием особых потоковых микропроцессоров, которые относятся к классу специализированных и будут рассмотрены в следующем семестре;

2) Специальной организацией вычислительного процесса и модификацией машинного языка низкого уровня в мультимикропроцессорных ансамблевых ВС, построенных на типовых микропроцессорах фон Неймана;

3) Созданием процессоров с избытком однотипных операционных блокови дополнением операционных систем потоковым способом организации вычислительного процесса (реализовано в отечественных потоковом процессоре ЕС2703 и суперЭВМ Эльбрус-2).

Цифровое моделирование в России есть: доказано в «НЕОЛАНТ»

Компания «НЕОЛАНТ» на основе многолетнего опыта информационного моделирования в России разработала собственную типологию цифровых моделей объектов промышленного предприятия. Основанием классификации является ключевая задача, для которой модель реализуется и используется, — от централизации инженерных данных по объекту до мониторинга процессов, моделирования физических и технологических процессов и обучения персонала.

В соответствии с типологией «НЕОЛАНТ» выделяется шесть типов информационных моделей (рис. 1).

Наиболее распространенными сегодня являются два первых типа: 3D-модель «Декорация» и инженерная 3D-модель. При этом они зачастую используются на этапе планирования и проектирования объектов, хотя могут эффективно применяться и для решения эксплуатационных задач.

Компания «НЕОЛАНТ» предлагает вашему вниманию примеры реальных проектов, представленных в виде видеороликов, наглядно демонстрирующих возможности некоторых типов информационных моделей.

Тип:

Пример: 3D-памятники Москвы (рис. 2).

Информационные 3D-модели около 40 исторических объектов столицы помогают Департаменту культурного наследия города Москвы в формировании и реализации государственной политики в области государственной охраны, сохранения, использования и популяризации объектов культурного наследия (памятников истории и культуры) народов Российской Федерации. Информационная система, созданная «НЕОЛАНТ», решает следующие задачи:

- сбор, накопление, хранение, поддержание в актуальном состоянии пространственной и атрибутивной информации об объектах историко-культурного опорного плана города Москвы;

- обеспечение удобного доступа к информации об объектах историко-культурного опорного плана города Москвы, в том числе об истории изменения их статуса;

- реализация возможности просмотра 3D-моделей объектов историко-культурного опорного плана города Москвы;

- формирование документов на основе данных историко-культурного опорного плана города Москвы.

Тип: информационная 3D-модель «Справочник».

Пример: информационные модели всех десяти российских АЭС (рис. 3).

Информационная модель атомной станции позволяет организовать мгновенный доступ к огромному единому хранилищу данных и документации с помощью наглядных 3D-моделей объектов. При этом по каждому энергоблоку насчитывается 2,5 тыс. томов документации, а каждая модель объекта содержит примерно 300-400 тыс. графических элементов.

Тип: прикладная информационная 3D-модель.

Пример: информационная система обеспечения вывода из эксплуатации энергоблоков Курской АЭС (рис. 4).

В основе системы — информационные 3D-модели объектов, к которым привязана атрибутивная информация, проектно-конструкторская документация, технологические схемы и т.д.

Система позволяет решить следующие прикладные задачи:

- сбор и визуализация данных радиационного мониторинга;

- разработка планов производства работ;

- имитационное моделирование опасных работ;

- расчет объемов демонтажа, дезактивации и образующихся РАО; и т.д.

Тип: прикладная информационная модель.

Пример: моделирование хода строительно-монтажных работ на заводе (рис. 5).

Интеграция 3D-моделей объектов завода с системами календарно-ресурсного планирования позволяет оптимизировать ход строительно-монтажных работ, отслеживать состояние строящихся объектов и соблюдение графика, контролировать субподрядчиков-строителей, получать техническую и договорную документацию прямо из 3D-модели. Кроме того, подобная прикладная информационная модель удобна для проведения совещаний и планерок — наглядный доступ к информации о ходе строительства избавляет участников встречи от необходимости анализировать отчеты и документы.

Тип: имитационная модель.

Пример: моделирование аварийных ситуаций на площадке размещения АЭС (рис. 6).

Выполненное «НЕОЛАНТ» моделирование потенциальных аварийных ситуаций на АЭС необходимо для обеспечения высокого уровня безопасности функционирования этих объектов. Проект реализован по заказу Института проблем безопасного развития атомной энергетики (ИБРАЭ) РАН.

Тип: имитационная модель/виртуальный тренажер.

Пример: моделирование технологии демонтажа, обучение операторов робототехники технологическим операциям (рис. 7).

Для демонтажа реакторной установки АМБ-100 Белоярской АЭС планируется использовать «безлюдную» технологию, то есть на площадке будет работать только робототехника. Имитационное моделирование позволило провести предварительную отработку технологии, выявить ряд проблем и выработать предложения по их решению. Созданная имитационная модель будет использоваться и для обучения операторов робота, а в дальнейшем она обеспечит безопасность проведения работ по выводу из эксплуатации энергоблока.

Цифровое моделирование объектов — блог для профессионалов! Стандарты, подходы к стоимости, детализация моделей, прикладные задачи.

I-model.lj.ru — присоединяйтесь!

По материалам компании «НЕОЛАНТ»